we want to create a small STM32F4 based Board (for example 10x5cm in size), with limited Pins/sockets…

this topic has not the the claim to be perfect… all the infos are on the WikiPage

WikiPage: http://wiki.midibox.org/doku.php?id=mnmlcore#design_concepts we can edit - one piece of information - and have to possibility to to compare different designs more ease

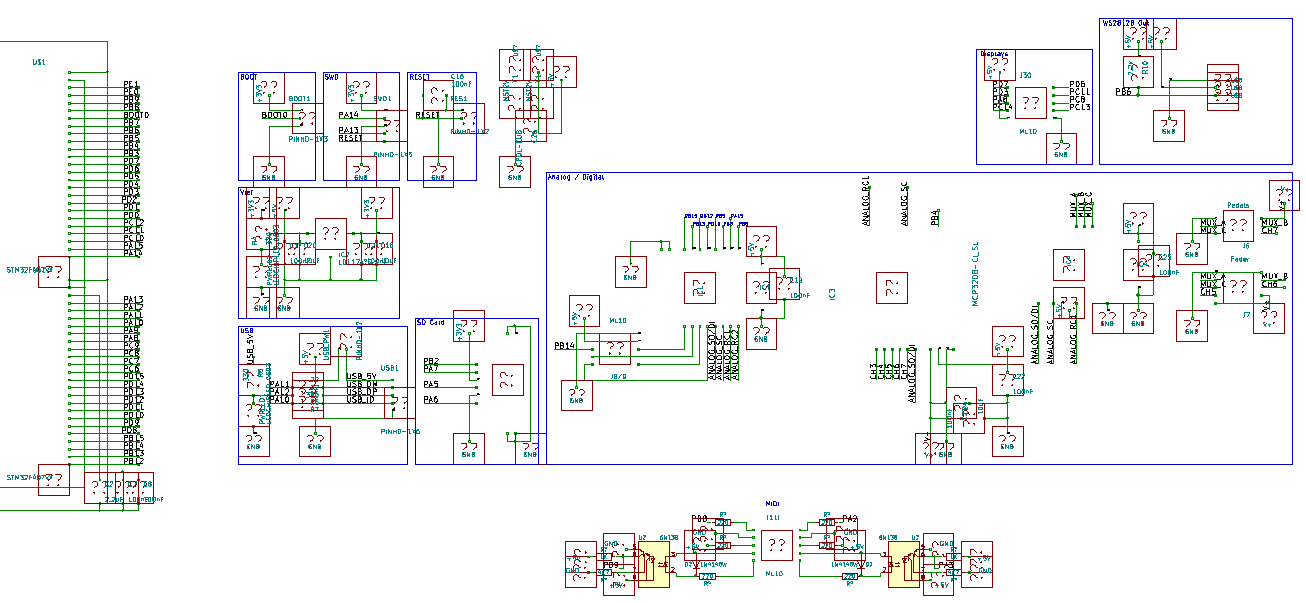

PCB: initial shematic/Board Layout (eagle): MinimalCore.zip taken from: (be aware that this files could be not ready for fabricate!!! - i take no response for any use of it!)

http://discourse.midibox.org/t/topic/20208

PCB: the eagle file above - ported 1:1 to Kicad 5 (which is still in 5.0.0 nightly): NewCoreSTM.zip that this file is not ready for PCB fabricate!)

DESIGN Concept:

discuss about how a small Core can be used on a small UI (small UI- less space) - also about the point that in most cases we need a midiport, and no optos are onboard till now… (except LPC17 and Core8)

please look into the wiki where i already pointed out my view of things

At first we should discuss the sense of that board. Should it be a pin-compatible replacement for the Core8? If yes, the feature-list is fixed.

Adding SMD-optos is no problem. My MIDI-PCB is already full-SMD.

Regarding PCB-manufacture: I order my PCBs at elecrow with very good results! So I’d suggest them.

You asked me about 3V3: The PCB has a 3V3 power plane as well as a GND plane.

In the wiki you wrote, that a programmer is needed. If I assemble those PCBs I’d program them with the MIOS bootloader so you don’t have to do it.

I’ll have a look into my designs and see if I can upload another eagle-file which contains the newest core design (with SMD crystal, etc.)

If having a small footprint the the main-goal in this design we should think about replacing the IDC headers with micromatch-headers. Smaller footprint and smaller connector-type on the cable-side.

Hello Guys,

Putting the stm on DIP40 package was just an idea!!! Something we have to talk about… I checked and the problem is not the design, a small 64pin stm32f405rg or an old stm32f103 can fit on DIP40 board. But replacing a PIC on a Core8 will require some level shifting to get the exact same pinout and port cause the core8 is fully 5V.

Yeah! was just an idea…

For me the minimum ports are

- the USB, the OTG FS

- J8 / 9 in 5V Spi for SRIO

- J16 / J19 an other SPI 5v / 3.3V switchable.

- J11 can be reduced to 1 or 2 MIDI ports

- by reducing the used port we can maybe put the sd card in SDIO instead of the regular SPI…(speed-up)

- we can maybe limit the LCD to a serial connection, no more // connection.

- reduce the number of I2C and Analog I/O.

- It will probably seem stupid, but I want to keep the CAN port on

About the USB, for the moment the Core uses the OTG FS, but there’s the extra OTG HS which can be used in FS and maybe limited to a HID and/or MIDI devices connection.

Just a thought but if redesigning the core would it be worth it to consider a newer processor? There is a lot of newer technology out there now.

I understand the reason not to as there is software dev involved.

1 Like

Just now, gerald.wert said:

I understand the reason not to as there is software dev involve

Because it’s a lot of work…

1 Like

11 minutes ago, gerald.wert said:

Just a thought but if redesigning the core would it be worth it to consider a newer processor? There is a lot of newer technology out there now.

I understand the reason not to as there is software dev involved.

for example?if it is pinsoftware compatible…but most cases not. spend my soft time more on fpga. for the bigger projects.for the smaller mios is enough. (for exsmple my triggermatrix will go fpga)

12 hours ago, gerald.wert said:

Just a thought but if redesigning the core would it be worth it to consider a newer processor? There is a lot of newer technology out there now.

I understand the reason not to as there is software dev involved.

Changing the uC, adding a new family is a lot of work, even if we stay in the STM32F family, e.g. from STM32F4 to STM32F7 between the 2 references ST changed the Low-Layer Driver, The F7 has HAL new driver now and MIOS32 was written around the old driver.

This is not easy to do mostly for the Bootloader part of the MIOS32. This is deep changes first, and a lot of support after to fix issues and bugs!

Here don’t want a new Core, just a smaller version of the existing one.

As I already said, we need a clever alternative to the existing big Cores, not a concurrent, Andy’s new wCore is already available for normal purpose, and I’ve got 4 running wCore for my experiences, I can say that’s a good one.

12 hours ago, Phatline said:

spend my soft time more on fpga

Interesting, which brand and model you use?

And the next question would be: Why? Does someone run the STM-Core at its limits? The STM32F407 is a beast and powerful and maybe already an overkill for “just midi”.

1 hour ago, FantomXR said:

And the next question would be: Why? Does someone run the STM-Core at its limits? The STM32F407 is a beast and powerful and maybe already an overkill for “just midi”.

Just maybe for the RAM, more RAM could be fine, but Yes everything else is enough. That’s the reason it should be fine to try to put the SD Card on SDIO, e.g. this will help to change presets in RAM quicker. And in the same time it will unload the J16 SPI of course.

1 hour ago, FantomXR said:

Does someone run the STM-Core at its limits?

Then yes I reach it sometimes but I always found a workaround for the moment. And this is enough

3 hours ago, Antichambre said:

Interesting, which brand and model you use?

xilinx… but dont know model… learning vhdl basics while trying to port the idea to it…since triggermatrix startedt years ago with max msp . and this was a paralell oriented structure. and im having still to much latency on my mios basrd version (its good in sequencer mode. but not tight enough to use it with drum triggers…) so model will be choosen on the teal demand of code

Then you want to replace the miniCore of your BLM by a FPGA?

my core in there in is not mini: http://wiki.midibox.org/lib/exe/detail.php?id=triggermatrix&media=phatline:tm_blm_gpio_extra08..jpg

a fpga with a arm in it for the code for most ui sd and other stuff i am not realy deep into… it will not be a fpga with a external mios remote…

the minimalcore is for all my small projects.

You connect the BLM directly to your main Core32? What is the use of the FPGA? handling the BLM part?

fpa: paralell calculate lots of trigger and all the live midi. drum sequencer. a arm should do the ui and copying ram patterns… all that is not timing critical and all where i dont know to handle on fpga…doesnt matter has not much to do with the minimal core

So, how do we proceed? What are the next steps for this project?

Hello,

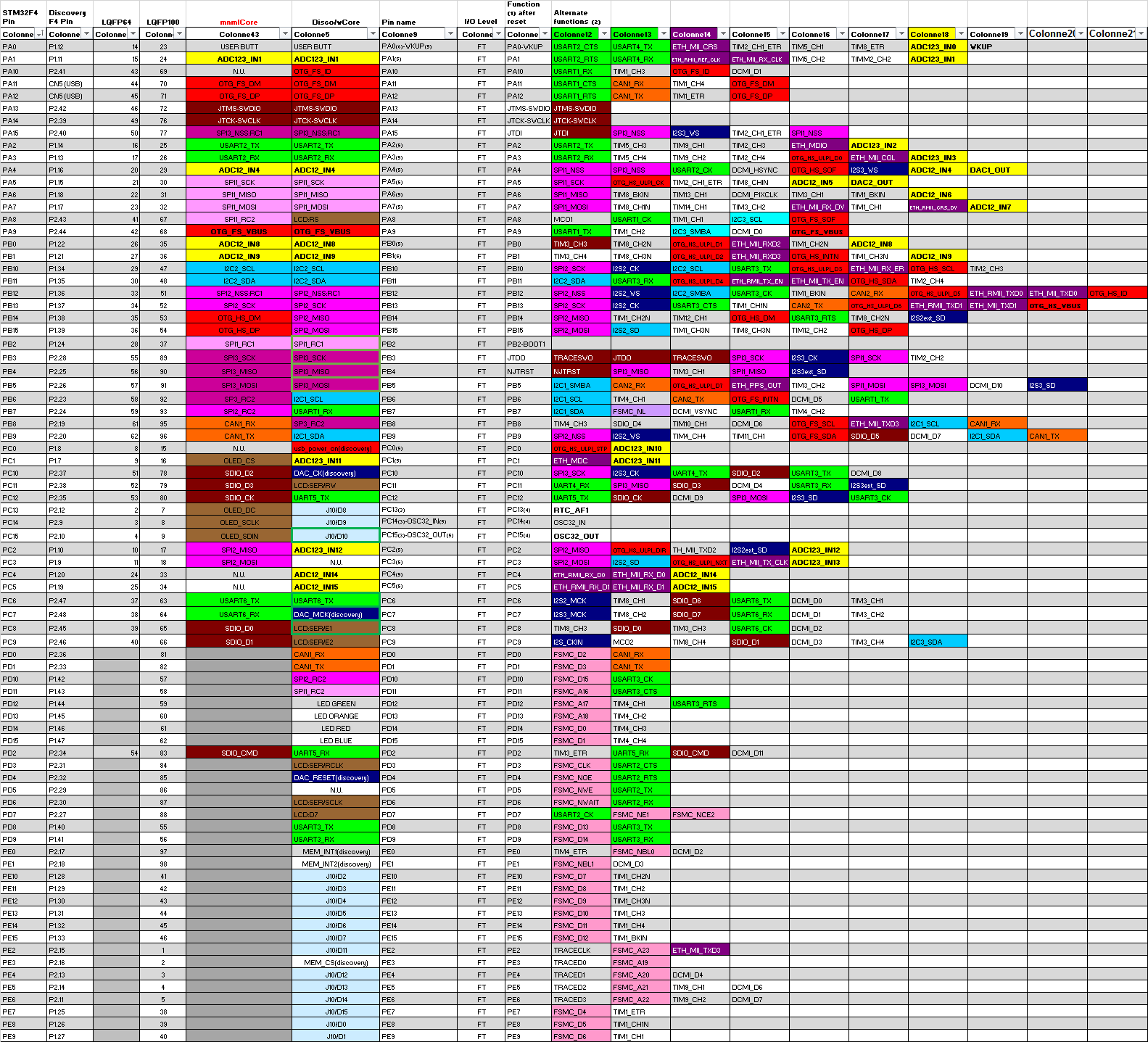

this is an excel chart I use for pin mapping, just as example.

Here I tried to map the pin of a STM32F405RG LQFP64 to the needed MIOS32 functions:

- 3 SPI and their respective RC, J16, J8/9 and J19.

- 2 UARTs (2 MIDI ports)

- 1 SDIO port for SD Card

- USB FS, static Upstream, but ID can be added for downstream

- USB HS in FS Mode for static Downstream.

- 4 ADC

- 1 I2C

- 1 CAN

- The User button

- No LED

- I kept some lines to connect a serial screen like OLEDs.

Just a basis for work, DMAs should also be taken into account!

Best regards

Bruno

PS: I can share the whole chart

Do we need to adapt the firmware when using a smaller STM or can we use it as is?

-just drawing the midi shematics… when the optos are on board a 10pin connector do the job… while your solution with external opto-board need only 6pin…

still have troubles with kicad 5, looses its part cache when saving, ours of work gone and so on… so cant say at the moment with space usage (got that ??)

1 hour ago, FantomXR said:

Do we need to adapt the firmware when using a smaller STM or can we use it as is?

Yes, some small adaptation have to be done in MIOS32, but not in App(except if it use a port we removed). Not very complicated if we stay in the same uC family, and everything can be tested before PCB design with awaveShare 405

Using a 405 instead of 407 makes no sense to me. 407 costs just 2€ more.